従来の10分の1の電力で動作する次世代スイッチの研究開発

物理限界を突破する画期的な技術を世界に先駆けて実現

情報科学研究科 情報エレクトロニクス専攻

集積システム講座

集積電子デバイス研究室・准教授

博士(工学)冨岡 克広

プロフィール

2003年、群馬大学工学部電気電子工学科卒。2005年、同大学院工学研究科電気電子工学修士課程修了。2008年、北海道大学大学院情報科学研究科情報エレクトロニクス専攻博士課程修了。2007年4月〜2009年3月、日本学術振興会特別研究員。2009年4月〜2009年9月、北海道大学グローバルCOE特別研究員。2009年10月〜2014年12月科学技術振興機構さきがけ専任研究者。2015年1月〜2016年5月、北海道大学大学院情報科学研究科助教およびJSTさきがけ相界面領域兼任。2016年6月より現職。2015年 文部科学大臣表彰・若手科学者賞、2016年 日本学術振興会賞、SSDM Paper Award受賞。

シリコンとは異なる物性を持つⅢ-Ⅴ族化合物ナノワイヤを用いたFET

集積電子デバイス研究室ではどのような研究をしているのですか。

冨岡 半導体結晶成長技術を基軸に、次世代集積システムの実現を目指した新しい集積デバイスの基盤研究を行っています。具体的には、(1)結晶成長の基礎と応用、(2)半導体ナノ構造の物性評価、(3)ナノワイヤなど新材料のデバイス応用です。

半導体ナノワイヤ材料と半導体ナノワイヤデバイスの開発を両軸とした開発を行っており、現在の主なテーマは「超低消費電力を実現する次世代スイッチ」の研究開発です。

半導体といえばシリコン(Si)を材料としたものが一般的ですが、近年はⅢ-Ⅴ族化合物を材料とした半導体の開発も進んでいます。Ⅲ-Ⅴ族化合物半導体にはシリコンとは異なる物性があり、例えば(1)バンドギャップが直接遷移型である、(2)電子移動度がシリコンよりも早いなど、シリコンにはない魅力があります。このため、発光ダイオードなどのデバイス応用にはⅢ-Ⅴ族化合物半導体が多く使われています。

こうした研究の背景には、スマートフォンやパソコンの頭脳となるマイクロプロセッサ・半導体集積回路の微細化・高集積化の限界という課題があります。発展し続ける情報化社会においては、コンピュータの性能を高度化するために集積回路のスイッチング素子(FET)の微細化・集積化が常に求められてきました。現在では、1センチ四方の面積に約20億個のFETが敷き詰められている状態ですが、FETのサイズとしてはこれが物理的限界と言われており、これ以上小さくしてもLSIの性能は向上しないと考えられています。特に問題なのが消費電力で、より多くの電力が必要になると同時に発熱の問題などが生じています。

それを本質的に解決するための技術として注目しているのが、Ⅲ-Ⅴ族化合物のナノワイヤを用いた新しいFETです。

シリコン基板上に異種集積させる技術の開発

Ⅲ-Ⅴ族ナノワイヤを用いた次世代スイッチとはどのようなものですか。

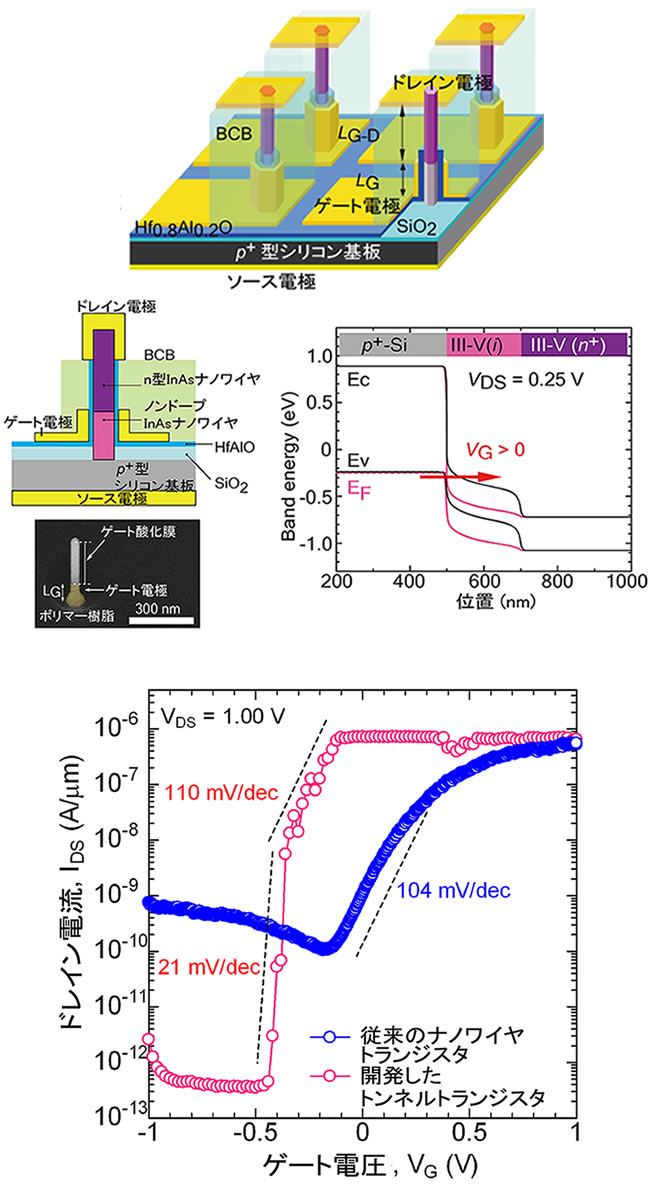

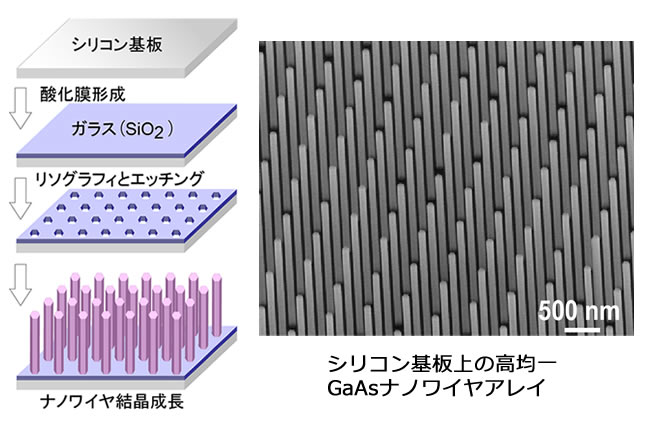

冨岡 有機金属気相成長(MOVPE)法を基盤としたナノメートルスケールの選択成長技術を使い、シリコン基板上にインジウムとヒ素の化合物によるナノワイヤを結晶成長させたものです(解説1)。従来のFETは平面に敷き詰めていますが、結晶成長技術を用いたナノワイヤは、基盤に対して垂直方向に林立させ、その1本1本にFETを作り込むことができます。縦方向に並べることで基板自体の微細化に頼らずとも集積度を上げることが可能になるのです。

もうひとつの特長は、シリコンの基板上にⅢ-Ⅴ族のナノワイヤを高均一に並べるための異種集積技術です。シリコンの最表面の原子配列をうまく置き換えて、Ⅲ-Ⅴ族のナノワイヤを縦方向に成長させ、高均一に集積できるような成長方法を世界に先駆けて開発しました。

これは、当研究室の前任の教授である福井孝志先生が長年に研究されてきた技術がベースになっています。リソグラフィによるトップダウンと結晶成長技術のボトムアップを融合した技術で、本研究ではシリコン基板上にⅢ-Ⅴ族のナノワイヤを成長させるという異種集積を実現しました。現在、ここまで正確に位置やサイズを制御できる結晶成長技術を持っている研究室は国内でもここしかありません。

スイッチング技術の理論限界を突破し、消費電力の90%以上を削減可能に

異種集積させた縦型FETにはどのようなメリットがあるのですか。

冨岡 もっとも大きな特徴は、従来のスイッチングの物理的限界を突破できることです。従来のFETは、スイッチング特性(サブスレッショルド特性:SS)に理論限界(60mv/桁)があるため、劇的な低消費電力化は不可能であるとされています。しかし、本研究では、ナノワイヤの異種集積で形成される新しい半導体接合界面をスイッチ素子に応用することで、FETの物理的限界を突破し、従来の消費電力を90%以上削減できる低電圧性能を達成しました(解説2)。

それを可能にしているのがシリコン基板とナノワイヤが接する境界面で起きる量子トンネル効果です。トンネル効果を使ったスイッチングは理論的には知られていましたが、境界面に原子を精緻に配列するのが難しく、なかなか実現できませんでした。私たちが開発した技術では、シリコン基板上にナノワイヤの縦型構造を形成すると同時に、境界面での欠損がほとんどない配列を実現したことで、トンネル電流をスイッチングに利用できるようになりました。

今後、これらの研究開発はどのように進んでいくのでしょうか。

冨岡 実用化への取り組みとしては、従来のFETと同じようにCMOSの構造を作ることです。CMOSはnチャネルとpチャネルとのMOSFETを相補的に利用する構造なのですが、そこをきちんと作ることが必要だと考えています。それができると回路を作ることもできるようになるので、そこが現在の課題です。相補型のトンネルFETは従来のものに比べてプロセスが複雑になるため、世界各国の研究機関で開発に取り組んでいるテーマです。

じつは、それに対しても解決策が見え始めています。思いのほかシンプルなアイディアで解決できそうなので、近いうちに技術的な道筋が見えてくるでしょう。

将来的には回路を組み込んだチップの形で製品化することを目指しています。超低消費電力で動くパソコンやスマホが可能になるだけでなく、体内に埋め込んで動作する小型デバイスといった医療分野での実用化も視野に入れています。

解説

解説1:ナノワイヤ異種集積技術

集積電子デバイス研究室の前教授・福井孝志氏が長年研究を続けてきたリソグラフィによるトップダウンと結晶成長技術のボトムアップを融合した技術を応用。位置・サイズを非晶質薄膜によるテンプレートの開口部で制御し、任意の位置に、任意のサイズの結晶を作成することができる。本研究では、シリコン基板最表面のガラス層に開口部を形成し、Ⅲ-Ⅴ族化合物(インジウムとヒ素の加工物)によるナノワイヤを結晶成長させ立体構造を作り上げた。ナノメートルの選択成長技術において、表面の原子配列を精緻に変化させることで、シリコンとⅢ-Ⅴ族化合物との異種集積が可能になった。

解説2:Si/3-Vヘテロ接合境界面によるトンネルFET素子の作製

シリコン基板とナノワイヤとの境界面を精緻に形成することで境界面の物理現象(トンネル電流)をスイッチングに利用することを可能にした。実験では、FETの理論限界を突破するサブスレッショルド特性を示し、ナノワイヤの特異な構造を応用することでトンネルFETの電流値をおよそ1000倍にする新しい技術・素子構造を実証した。